УДК 681.004.6

# НЕПРЕРЫВНЫЙ ПОДХОД К ПОСТРОЕНИЮ ТЕСТОВ РЕЗИСТИВНЫХ МОСТИКОВЫХ НЕИСПРАВНОСТЕЙ

© 2011 г.

Н.И. Кащеев, Ф.М. Подъяблонский

Нижегородский государственный технический университет им. Р.Е. Алексеева

nikolay.kascheev@gmail.com

Поступила в редакцию 17.02.2011

Развивается подход к построению тестов цифровых схем, в основе которого лежит применение непрерывных моделей дискретных устройств. В рамках данного метода решается задача поиска тестов для мостиковых неисправностей последовательностных схем. При этом используются обобщенная модель представления дефекта, конкретизируемая посредством резистивной модели мостиковой неисправности, а также алгоритмы моделирования последовательностной схемы с помощью непрерывных функций. Описанные алгоритмы и методы реализованы в программном комплексе автоматической генерации тестов. Представлены результаты апробации для ряда схем набора ISCAS'89.

*Ключевые слова*: резистивная модель, мостиковые неисправности, цифровые схемы, последовательностные схемы, автоматическое построение тестов, моделирование неисправностей, непрерывные модели.

#### Ввеление

В связи с высокой степенью интеграции и миниатюризации современных цифровых вычислительных устройств большая часть дефектов схем приходится на неисправности мостикового типа. Элементы в схемах располагаются ближе друг к другу, увеличивается число слоев в схемах, что и повышает вероятность возникновения неисправностей данного вида. Именно поэтому все больше внимания при разработке методов и алгоритмов тестирования схем уделяется мостиковым неисправностям. Тестовые наборы, построенные с использованием классических методов генерации тестов, в основе которых лежит константная модель неисправности, не обеспечивают достаточного покрытия возможных дефектов схем. Требуются новые более реалистичные модели неисправностей, а также методы и алгоритмы генерации тестов, использующие их.

В данной работе задача построения тестов для мостиковых неисправностей последовательностных схем решается с использованием обобщенной модели неисправности (модели неисправного блока) и непрерывного подхода к моделированию схемы и поиску тестовых наборов. Этот метод подразумевает, что каждый логический элемент схемы моделируется непрерывными продолжениями логических функций.

Основная идея данного подхода заключается в построении непрерывной целевой функции, характеризующей степень различия значений на выходах исправной и неисправной схем, параметрами которой являются сигналы на первичных входах схем. Целевая функция принимает свое максимальное значение, равное 1, если значения на выходах исправной и неисправной схем отличаются хотя бы в одной позиции, т.е. в том случае, когда входной набор является тестовым. Таким образом, задача построения теста сводится к задаче максимизации целевой функции.

Обобщенная модель неисправности подразумевает, что дефект преобразует некую область схемы в отдельный неисправный блок, имеющий несколько входов и выходов. Размер блока и соответственно моделируемая им часть схемы зависят от выбора конкретного метода представления неисправности, используемого при построении тестов. В самом простом случае такой блок будет включать в себя элементы схемы, выходами которых являются линии, вовлеченные в неисправность. В более общем случае неисправный блок может содержать элементы, расположенные на пути распространения сигнала от места неисправности до выходов схемы, и даже элементы, находящиеся на линиях обратной связи, если таковые образуются из-за присутствия мостиковой неисправности. Таким образом, неисправный блок реализует некоторую функцию, вид которой зависит от конкретного алгоритма моделирования дефекта. В рамках данной работы для конкретизации обобщенной модели неисправностей используется модель резистивной мостиковой неисправности.

Рассмотренные алгоритмы и методы реализованы программно в системе автоматического поиска тестовых наборов. Представлены результаты работы для ряда последовательностных схем набора ISCAS'89.

## Модель резистивной мостиковой неисправности

В рамках данной работы общий подход к решению задачи построения тестов цифровых схем и моделирования неисправностей детально рассмотрен и проработан для мостиковых неисправностей в последовательностных схемах.

Моделирование неисправности производится посредством замены части исправной схемы, прилегающей к месту дефекта, на неисправный блок, размеры и реализуемая функция которого определяются исходя из способа представления неисправности. В данной работе в качестве метода описания функционирования схемы в присутствии неисправности применяется так называемая модель резистивной мостиковой неисправности, предложенная в [1, 2].

Большинство моделей мостиковых неисправностей, описывающих дефект на логическом уровне представления схемы, основаны на предположении нулевого (0 Ом) сопротивления в месте перемыкания линий, вовлеченных в неисправность. Лишь несколько из существующих моделей представляют резистивные мостиковые неисправности.

Задачи моделирования резистивных мостиковых неисправностей и автоматического построения тестов для их диагностики осложняет тот факт, что значение сопротивления  $R_{sh}$  между двумя линиями схемы, замкнутыми в результате дефекта, заранее неизвестно. Перемыкание линий приводит к установлению на них промежуточных значений напряжения (находящихся между  $0 \ B$  и  $V_{DD}$  ). Последующий элемент схемы G, для которого линии, вовлеченные в неисправность, являются входными, интерпретирует эту промежуточную величину как 0 или 1 в зависимости от значения порогового напряжения на входе  $Th_G$ . Напряжение на линиях, вовлеченных в неисправность, и соответственно интерпретируемые логические значения на них зависят от сопротивления  $R_{sh}$ . Для достаточно высоких зна-

чений  $R_{sh}$  последующие элементы интерпретируют напряжение на рассматриваемых линиях так же, как и в отсутствие неисправности. В общем случае элемент G интерпретирует значение сигнала на линии ошибочно для значений  $R_{sh}$ , меньших некоторой граничной величины  $R_G$ , называемой критическим сопротивлением элемента G. Значение данной величины зависит от рассматриваемой неисправности, типа элемента, а также от логических значений на входах элементов, выходами которых являются линии, вовлеченные в неисправность. Для данной неисправности существует m > 0 критических сопротивлений  $R_0 = 0 \Omega < R_1 < \dots < R_m < \infty$ .  $R_{\max} = R_m - 1$ максимальное критическое сопротивление. Такой подход к рассмотрению мостиковой неисправности позволяет выделить интервалы значений  $R_{sh}[R_i, R_{i+1}], i = 0, (m-1)$  (для m критических сопротивлений существует таких секций), и однозначно определить логические значения на входах элементов, следующих за местом неисправности, для значений  $R_{sh}$ , принадлежащих конкретному интервалу.

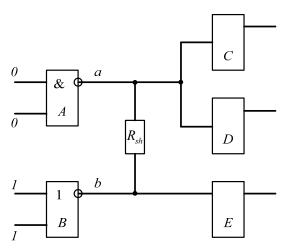

Рис. 1. Пример схемы

Рассмотрим пример схемы, представленный на рис. 1. Линии схемы a и b перемкнуты в результате неисправности, линия a является выходом элемента A (2И-НЕ), линия b — выходом элемента B (2ИЛИ-НЕ). Предположим, что на оба входа элемента A подается значение логического 0, а на оба входа элемента B — значение логической 1. B этом случае в отсутствие неисправности логические значения на линиях определяются следующим образом: на линии a — логическая 1, на линии b — логический 0. B случае рассмотрения мостиковой неисправности, возникшей между линиями a и b, значения напряжения на данных линиях  $V_A$  и  $V_B$  будут

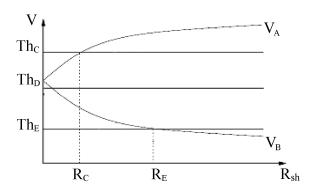

зависеть от сопротивления в месте перемыкания  $R_{sh}$ . При  $R_{sh}=0$  значения  $V_A$  и  $V_B$  будут одинаковы, при  $R_{sh}=\infty$   $V_A=V_{DD}$  и  $V_B=0$  (этот случай равносилен отсутствию неисправности). Зависимость величин  $V_A$  и  $V_B$  от значения  $R_{sh}$  представлена графиком на рис. 2 [2].

Рис. 2. График зависимости  $V(R_{sh})$

Итак, в результате неисправности на линиях устанавливаются некоторые промежуточные значения напряжений. Рассмотрим, каким образом последующие элементы (в данном случае С, D и E) интерпретируют эти значения. Линия a является входом для элементов C и D, а линия b – входом элемента E. Типы этих элементов, а также наличие или отсутствие у них других входов кроме линий, вовлеченных в неисправность, не имеют значения. Предполагается, что для каждого из этих элементов определено пороговое значение напряжения на входе Th. В общем случае эта величина может быть различна для различных входов элемента, для элементов различных типов, реализующих одну и ту же функцию. Интерпретация напряжения на входе однозначно зависит от данной величины: значения напряжения, большие, чем Th, воспринимаются как логическая 1, все меньшие значения – как логический 0. На графике (рис. 2) пороговые значения элементов обозначены  $Th_C$ ,  $Th_D$ , и  $Th_E$ .

Рассмотрим элемент C. Для данного сопротивления  $R_{sh}$  элемент интерпретирует входное значение как логический 0 или логическую 1, в частности, существует некоторое значение сопротивления  $R_C$ , называемое критическим сопротивлением, такое, что при  $R_{sh} < R_C$  значение на входе интерпретируется как логический 0, а при  $R_{sh} > R_C$  — как логическая 1. Таким образом, неисправность может быть активизирована и распространена через элемент C только при сопротивлении  $R_{sh} < R_C$ , в противном случае неисправность не повлияет на логическое

значение линии. Поскольку для критического сопротивления верно равенство  $V_a(R_C) = Th_C$ ,  $R_C$  может быть определено по графику (рис. 2) как пересечение кривой  $V_A$  и прямой  $Th_C$ .

Для элемента D прямая  $Th_D$  лежит ниже кривой  $V_A$ . Это означает, что для любого значения  $R_{sh}$  элемент D воспримет значение на линии a как логическую 1, и критического сопротивления не существует, следовательно, эффект неисправности не может быть распространен через этот элемент ни при каком значении  $R_{sh}$ .

Для элемента E критическое сопротивление  $R_E$  существует, и ошибочное значение (логическая 1) будет интерпретировано на входе при  $R_{sh} < R_E$ .

Конкретные значения критических сопротивлений могут быть получены из справочных таблиц, построенных в результате моделирования схем с использование таких симуляторов, как, например, SPICE [3], а также вычислены с помощью формул [1].

## Моделирование последовательностной схемы

Построение тестового набора состоит в решении задачи поиска максимума непрерывной функции, которая получается в результате сравнения выходов исправной логической сети и сети с неисправностью. Рассмотренная выше модель мостиковой неисправности внедряется в модель последовательностной схемы, в результате получается логическая сеть с внедренной неисправностью [4–9].

В качестве модели логической сети, в основе которой лежит синхронная последовательностная схема, используется итеративный логический массив. Это представление исходной схемы в виде последовательности соединенных между собой временных кадров. Под временным кадром подразумевается последовательностная схема, преобразованная таким образом, что она не содержит триггеров и имеет дополнительные входные и выходные линии, моделирующие линии текущего и следующего состояния исходной последовательностной схемы.

Процесс преобразования схемы в итеративный логический массив заключается в соответствующем представлении триггеров, присутствующих в схеме. Каждый D-триггер (триггер задержки) заменяется на комбинационный элемент с двумя входами и двумя выходами. При этом дополнительный вход модифицированного триггера будет хранить его текущее состояние (будет являться псевдопервичным входом сети),

а дополнительный выход будет линией следующего состояния (псевдопервичный выход). Линия следующего состояния становится линией текущего состояния в следующем такте работы синхронной схемы.

В результате преобразования исходная схема превращается в комбинационную, в которой наряду с первичными входами и выходами присутствуют линии псевдопервичных входов и выходов. На линии псевдопервичных входов подаются сигналы, соответствующие текущему состоянию последовательностной схемы, а с линий псевдопервичных выходов снимаются значения следующего состояния схемы. Итеративный логический массив формируется из нескольких временным кадров путём соединения псевдопервичных выходов і-го временного кадра с одноименными псевдопервичными входами (i+1)-го временного кадра. Конструкция из п временных кадров является моделью функционирования синхронной последовательностной схемы на протяжении п тактов ее работы.

#### Результаты

Представленный вариант решения задачи построения тестов для резистивных мостиковых неисправностей последовательностных схем реализован программно и апробирован на некоторых схемах набора ISCAS'89. Для каждой схемы случайным образом были выбраны 10 000 мостиковых неисправностей (если возможно), не образующих обратных связей в схеме. Испытания проводились на машине, имеющей следующие характеристики: 1.6 GHz CPU, 512 MB RAM. В таблице приведены полученные результаты работы. Таблица содержит: название схемы; число рассмотренных неисправностей; число неисправностей, для которых тест был найден (хотя бы для одного из значений сопротивления мостиковой неисправности); время работы программы.

#### Заключение

В данной работе общий подход к моделированию неисправностей различного типа, а также универсальный метод построения тестов, основанный на использовании непрерывной модели цифровой схемы, использованы при разработке и построении системы автоматической генерации тестовых наборов для мостиковых неисправностей последовательностных схем. Представлены результаты работы программного комплекса на ряде схем набора ISCAS'89, демонстрирующие применимость и эффективность предложенных алгоритмов.

#### Список литературы

- 1. Renovell M., Huc P., Bertrand Y. The Concept of Resistance Interval: A New Parametric Model for Realistic Resistive Bridging Fault // IEEE VLSI Test Symp. 1995. P. 184–189.

- 2. Engelke P., Polian I., Renovell M., Becker B. Simulating resistive bridging and stuck-at faults // Int'l Test Conf. 2003. P. 1051–1059.

- 3. Lee C., Walker D.M.H. PROBE: A PPSFP simulator for resistive bridging faults // VLSI Test Symp. 2000. P. 105–110.

- 4. Sar-Dessai V., Walker D.M.H. Accurate Fault Modelling and Fault Simulation of Resistive Bridges // Int. Symp. Defect and Fault Tolerance in VLSI Systems. 1998. P. 102–107.

- 5. Renovell M., Huc P., Bertrand Y. CMOS bridge fault modeling // IEEE VLSI Test Symp. 1994. P. 392–397.

- 6. Kano H. Test pattern generation for logic networks by real number logic simulation // AUTOTESTCONF'79. 1979. P. 168–178.

- 7. Миндров А.Е., Кащеев Н.И. Использование непрерывной модели схемы для генерации тестов // Simulation and CAD systems. 1989. P. 47–50.

- 8. Danilov S., Kasheev N. Automatic test pattern generation using continuous approach // Proceedings of Internetional Scientific conf. «Informatics, Mathematical Modelling & Design in the technics, controlling & education (IMMD) '2004», Vladimir city, VGU, 2004. P. 187–192.

- 9. Кащеев Н.И., Белобородов В.В. Использование непрерывной оптимизации для генерации тестовых наборов // Системы обработки информации и управления, Н. Новгород, 2001. Вып. 7. С. 21–25.

Результаты работы программы генерации тестов

Таблица

| Схема | Количество рассмотренных<br>неисправностей | Количество покрытых<br>неисправностей | Время, с |

|-------|--------------------------------------------|---------------------------------------|----------|

| s27   | 29                                         | 29                                    | 1.52     |

| s208  | 5334                                       | 5112                                  | 310.42   |

| s298  | 7973                                       | 7689                                  | 237.55   |

| s386  | 10000                                      | 9357                                  | 286.24   |

| s641  | 10000                                      | 9870                                  | 315.23   |

| s953  | 10000                                      | 9763                                  | 925.15   |

# CONTINUOUS SIMULATION APPROACH TO THE CONSTRUCTION OF TESTS FOR RESISTIVE BRIDGING FAULTS

N.I. Kashcheev, F.M. Podyablonsky

An approach to construction of digital circuit tests on the basis of continuous models of discrete devices is developed. The method is used to solve the problem of finding test sets for bridging faults of sequential circuits. A generalized fault model representation specified with a resistive model of a bridging fault is used together with simulation algorithms of a sequential circuit using continuous functions. The described algorithms and methods are implemented in the software package of automated test construction. The approbation results for some ISCAS'89 benchmark circuits are presented.

Keywords: resistive model, bridging faults, digital circuits, sequential circuits, automated test construction, fault simulation, continuous models.

.